Table of Contents

We want to hear from you! Take our quick AI survey and share your insights on the current state of AI, how you’re implementing it, and what you expect to see in the future. Learn More

Applied Materials has revealed chip wiring innovations that will help address challenges in the way of energy-efficient computing.

The use of new materials in chip wiring will enable two-nanometer node manufacturing, where the width between circuits is around two billionths of a meter apart. These innovations will reduce resistance in wiring as much as 25% and new materials will reduce chip capacitance by up to 3%.

Chip makers are using the advances in the manufacturing of logic chips now and memory chip makers (who make dynamic random access memory, or DRAM) are evaluating it now for improved 3D chip stacking.

The mission is to ultimately enable equipment that can build a trillion-transistor chip such as a graphics processing unit, according to a story in the IEEE Spectrum journal. It’s tough to keep up with the pace of Moore’s Law, the 1965 prediction by former Intel CEO Gordon Moore that holds the number of components on a chip will double every couple of years. Instead of getting smaller, chips are getting bigger and multiple chips are being integrated into a single solution using advanced packaging.

The good thing is that the chip industry has been able to get a three times improvement every two years over the past 15 years. To do this, it needs to keep developing new materials, said Alex Jansen, director of product marketing at Applied Materials, in an interview with VentureBeat.

“To continue this, we need new materials,” Jansen said. “There are several ways: patterning, transistors, wiring and advanced packaging. We are focusing on wiring.”

And wiring is important. Recent chips have more than 60 miles of copper interconnect, 18 metal layers and four or five critical layers, he said. Every chip is a giant 3D network of wires, Jansen said.

Applied Materials is the biggest maker of semiconductor manufacturing equipment, and it revealed the advances at the Semicon West event in San Francisco today. The company said the materials engineering innovations are designed to increase the performance-per-watt of computer systems by enabling copper wiring to scale to the 2nm logic node and beyond.

“The AI era needs more energy-efficient computing, and chip wiring and stacking are critical to performance and power consumption,” said Prabu Raja, president of the Semiconductor Products Group at Applied Materials, in a statement. “Applied’s newest integrated materials solution enables the industry to scale low-resistance copper wiring to the emerging angstrom nodes, while our latest low-k dielectric material simultaneously reduces capacitance and strengthens chips to take 3D stacking to new heights.”

Overcoming the physics challenges of classic Moore’s Law scaling

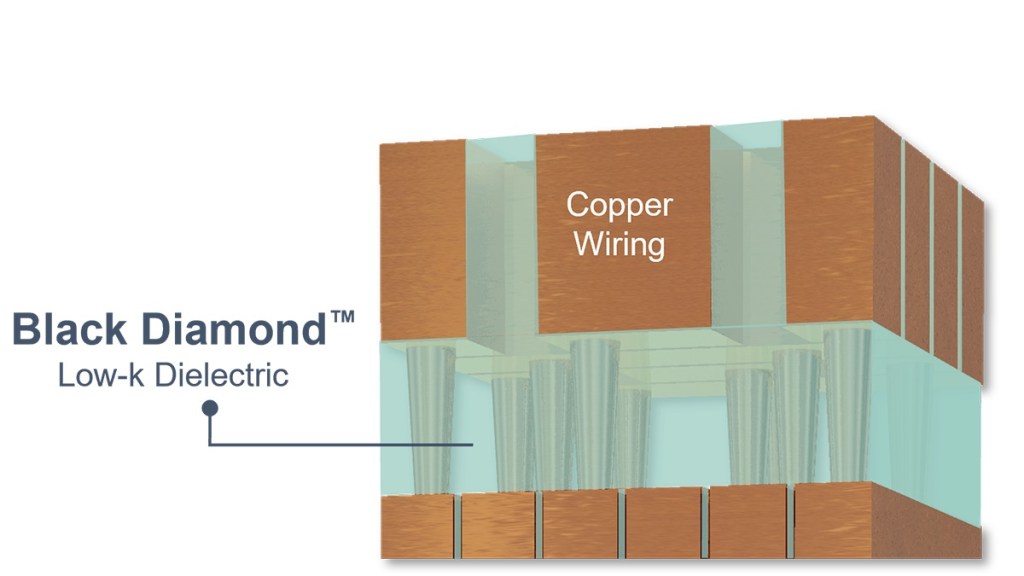

Today’s most advanced logic chips can contain tens of billions of transistors connected by more than 60 miles of microscopic copper wiring. Each layer of a chip’s wiring begins with a thin film of dielectric material, which is etched to create channels that are filled with copper.

Low-k dielectrics and copper have been the industry’s workhorse wiring combination for decades, allowing chipmakers to deliver improvements in scaling, performance and power-efficiency with each generation.

However, as the industry scales to 2nm and below, thinner dielectric material renders chips mechanically weaker, and narrowing the copper wires creates steep increases in electrical resistance that can reduce chip performance and increase power consumption.

Enhanced Low-k dielectric reduces interconnect resistance and strengthens chips for 3D stacking

Applied said its Black Diamond material has led the industry for decades, surrounding copper wires with a low-dielectric-constant – or “k-value” – film engineered to reduce the buildup of electrical charges that increase power consumption and cause interference between electrical signals.

Applied today introduced an enhanced version of Black Diamond, the latest in the company’s Producer Black Diamond PECVD (plasma-enhanced chemical vapor deposition) family. This new material reduces the minimum k-value to enable scaling to 2nm and below, while offering increased mechanical strength which is becoming critical as chipmakers and systems companies take 3D logic and memory stacking to new heights.

Ajay Bhatnagar, managing director of product marketing, said in an interview with VentureBeat that the dielectric deposition group has been working on the capacitance side of the problem.

“We are very excited about introducing recent innovations in what we call Enhanced Black Diamond,” he said.

It’s a new chemical vapor deposition material used for shoring up trenches and insulating the wires from binary materials.

“You can think of this as a matrix into which this mesh of copper wiring is embedded into,” Bhatnagar said. “We’re surrounding the wires with very low-k dielectric constant. And the film is really engineered to reduce the buildup of electrical charges that can increase power consumption and cause interference between the electrical signals.”

“Today, we are introducing a new class of these Black Diamonds that we call enhanced. The main benefit is this new material reduces the key value of the dielectric constant, which allows customers to scale to two nanometers and below,” Bhatnagar said. “But at the same time, it increases the mechanical strength, which is now becoming really really critical. As chip makers and system companies take 3D logic and memory stacking to new heights, mechanical strength and a value become very critical.”

He said the enhanced Black Diamond technology is being now adopted by all leading logic and memory chip makers.

“One of the biggest challenges for us in the low-k material side for this matrix has to be to break the trade off between dielectric constant and mechanical strength,” Bhatnagar said. “Customers want to push lower and lower dielectric constant because that helps in terms of reducing the capacitance and the signal noise between the lines.”

“There is a trade off between getting the dielectric constant down, as well as increasing the mechanical strength of the dielectric. This new material that we’ve engineered at the molecular level has broken this trade off that existed. What we’ve done with molecular engineering in terms of this matrix is created a new low-k material, which has broken that trade off.”

“We’re trying to lower the capacitance, and one way to do that is to lower what we call the dielectric constant. Capacitance is directly proportional to this constant. We’re lowering that and at the same time we are increasing the mechanical strength,” said Bhatnagar. “Typically, there is a tradeoff with that. So with this new molecule that we put into the enhanced Black Diamond, we have been able to break this tradeoff and move the curve.”

To scale chip wiring, chipmakers etch each layer of low-k film to create trenches, then deposit a barrier layer that prevents copper from migrating into the chip and creating yield issues. The barrier is then coated with a liner that ensures adhesion during the final copper reflow deposition sequence, which slowly fills the remaining volume with copper.

As chipmakers further scale the wiring, the barrier and liner take up a larger percentage of the volume intended for wiring, and it becomes physically impossible to create low-resistance, void-free copper wiring in the remaining space.

Today, Applied Materials introduced its latest IMSTM (Integrated Materials Solution) which combines six different technologies in one high-vacuum system, including an industry-first combination of materials that enables chipmakers to scale copper wiring to the 2nm node and beyond. The solution is a binary metal combination of ruthenium and cobalt (RuCo), which simultaneously reduces the thickness of the liner by 33 percent to 2nm, produces better surface properties for void-free copper reflow, and reduces electrical line resistance by up to 25% to improve chip performance and power consumption.

The focus has been to make the wiring better and improve the dielectric on the wiring. As the features shrink, it gets harder to put copper wiring into the trenches without creating what are known as voids, where there is a section that didn’t get copper into it. This impacts resistance and yield as well. Resistance keeps coming back as a problem with each generation of chips.

Now the company is switching to a combination of ruthenium and cobalt as the liner between the copper and the film. It can reduce the thickness of the liner by up to 33%. The result is there is more room for the copper in the trench, and that widens the effective wire, which lowers the resistance. Performance goes up. The width of these sections in the structure is microscopic and it results in better yields.

The new Applied Endura Copper Barrier Seed IMS with Volta Ruthenium CVD (chemical vapor deposition) is being adopted by all leading logic chipmakers and began shipping at the 3nm node. An animation can be viewed here.

“While advances in patterning are driving continued device scaling, critical challenges remain in other areas including interconnect wiring resistance, capacitance and reliability,” said Sunjung Kim, VP and head of the foundry development Team at Samsung Electronics, in a statement. “To help overcome these challenges, Samsung is adopting multiple materials engineering innovations that extend the benefits of scaling to the most advanced nodes.”

“The semiconductor industry must deliver dramatic improvements in energy-efficient performance to enable sustainable growth in AI computing,” said Y.J. Mii, EVP and co-COO at TSMC, in a statement. “New materials that reduce interconnect resistance will play an important role in the semiconductor industry, alongside other innovations to improve overall system performance and power.”

A growing wiring opportunity

Applied is the industry leader in chip wiring process technologies. From the 7nm node to the 3nm node,

interconnect wiring steps have approximately tripled, increasing Applied’s served available market opportunity by more than $1 billion per 100,000 wafer starts per month (100K WSPM) of greenfield capacity, to approximately $6 billion.

Looking ahead, the introduction of backside power delivery is expected to increase Applied’s wiring opportunity by another $1 billion per 100K WSPM, to approximately $7 billion.

One research initiative that Intel recently talked about focused on making wiring better through the backside of a chip, which normally isn’t used for wiring. This architectural change takes power lines from the front of the chip to the backside, where the wiring needs to be thicker. But frontside wiring needs improvements as well, and so these improvements are all happening in parallel, Jansen said.

The addition of backside wiring reduces complexity and that helps get more efficient routing and better performance and power consumption, Jansen said. But the frontside improvements are also necessary to enable scaling.

About 20 years ago, the wiring moved away from aluminum to dielectrics and copper. To drive more performance every year, the industry has been adding more materials to create stronger wires that are more energy efficiency. The chip equipment etches trenches and vias into the film on the chip surfaces, and then ultimately fills those gaps with copper for wiring. Copper is the main way to conduct electrons through the chip. Now the materials serve as a barrier between the copper and the dielectric so they don’t contaminate each other.

“Without materials innovation, the barriers and the liners are starting to occupy more and more of that trench volume. So this scaling creates a couple of different challenges. As copper wires shrink, resistance goes up. This is sort of a basic physics (fact). Thinner wires are going to create higher resistance. There isn’t really a good way around that,” Jansen said.

He added, “And so what we’re trying to do is improve the amount of that wire that is dedicated to convert. Secondly, as these things shrink, the wires are getting closer and closer together. And so there’s less space for the dielectric that is surrounding them. And as a result, you have electrical crosstalk. You can get signal delays, distortion, and altogether this cost in performance and power consumption. So that’s the opposite of what we’re trying to do.”

To make enhancements for demanding AI chips, the performance and efficiency has to keep getting better.

The new chip wiring products, along with other materials engineering innovations for making future AI chips, will be discussed at Applied’s Semicon West 2024 Technology Breakfast.

Better GPUs and AI chips

All of this work is aimed at making better GPUs and other AI chips that can handle the demands of the future, the Applied Materials spokesmen said. They see these wiring developments as helping the chip industry stay on the path of three times improvement every two years for energy efficiency.

“This is an enabling technology for 2nm and beyond,” Jansen said.

Bhatnagar added that stacking memory chips is necessary for feeding data to AI processors, and high mechanical strength is needed for the 3D stacking ability. The tech here enables the chips to reach high computing performance without melting down.

“That is one of the reasons we are driving these materials — because of the AI requirements for high-bandwidth memory,” Bhatnagar said.

As a result, Jansen said, “I think the cadence at which new technologies continue to extend Moore’s Law and the densification of the transistors per area is aligned with that” research in the estimates around reaching a trillion-transistor GPU. Nvidia’s Blackwell has about 208 billion transistors on it. AMD will be joining Applied Materials at its event his week.

Source link